̫ƽ��Ƽ� ��ҵ

AI��Сʱ���оƬ��Խ���࣡�ȸ�AlphaChip��Nature������Ƴ������콢TPU

����Ԫ

���ϱ༭��̫ƽ��Ƽ�

�����ڣ�2024-09-28 00:15

����Ԫ

���ϱ༭��̫ƽ��Ƽ�

�����ڣ�2024-09-28 00:15

-

�ȸ��Ƴ�AIϵͳAlphaChip����Сʱ�����оƬ���֣���Ӧ����TPU��CPU��ȫ��Ӳ����AlphaChipͨ��ǿ��ѧϰѧϰ��������ѵ�оƬ���֣����ڶ�ʱ�������ɳ�Խ����ˮƽ�IJ��֡��ȸ��ŶӶ�����һֱ�����ڸ���Ŀ������������ϸ������Ԥѵ�����㡣AlphaChip���ı�����оƬ������̣�������������������������

|

�����оƬ��AI�ڿƼ����ˣ� ���ڸոգ��ȸ�DeepMind�Ƴ���ΪAlphaChip��AIϵͳ��

������������Ƚ������ڹ���AIģ�͵�TPU�������������ĵ�CPU��������ص��ڶ����������˹㷺Ӱ�졣 �ڹȸ�������оƬ����У�����ȡ���˳�ɫ��Ч��������AxionоƬ��һ�ֻ���Arm ��ͨ����������CPU����

AlphaChip���оƬ���õ���ǿ��ѧϰ��ԭ���� Ҳ����˵��оƬ������ƶ�����˵��һ����Ϸ������AlphaGoһ����������Ϸ�У�ѧϰ�����Ƴ���õ�оƬ���֡� ��Сʱ�ڣ����������ɳ�������ˮƽ������������ר���൱��оƬ�����ˡ� ���ڣ����Ѿ�������ƶ��TPUоƬ��TPU v5e��TPU v5p��Trillium�������Ҹ�����ר����ȣ�AlphaChip���õĿ���Խ��Խ�࣬�߳�Ҳ���������ࡣ �������꣬�ȸ���TPUȫ��AI��� ��ʵ�ȸ�������AI���Ѿ����ֶ����ˡ� ����2020�꣬�ŶӾͷ�����һƪԤӡ�����ģ������˹ȸ��ȫ��ǿ��ѧϰ�������������оƬ���֡�

������2021�꣬�������������Nature�ϣ����ҽ����˿�Դ��

���Դ��״η���������������ȸ��ڲ�һֱ�ڶ������иĽ��� ���죬�Ŷӷ�����Nature��¼����ϸ�����˾��巽���������оƬ��������Ӱ�졣 ͬʱ�����ǻ�������һ��Ԥѵ���ļ��㣬������ģ��Ȩ�أ�����ģ������ΪAlphaChip�� �ȸ��ʾ��AlphaChip���������ڽ����ʵ���繤�����ǿ��ѧϰ����֮һ��

����Сʱ�ڣ����Ϳ������ɳ��˻����Ƶ�оƬ���֣�������Ҫ�������ܻ����µ����ࡣ����Ƶ�оƬ���֣��Ѿ�������������ص�оƬ�У������������ĺ��ƶ��绰�� Ϊ�����TPU���֣�AlphaChip����������ǰ�����ĸ���оƬģ���Ͻ���ʵ��������Ƭ�Ϻ�Ƭ������ģ�顢�ڴ�����������ݴ��仺��������һ���̱���ΪԤѵ���� Ȼ���Ŷ��ڵ�ǰ��TPUģ��������AlphaChip�������ɸ������IJ��֡� ��֮ǰ�ķ�����ͬ��AlphaChip�ڽ������оƬ��������ʱ��ø��á����죬����������ר�ҵĹ�����ʽ�� ����ÿһ���µ�TPU�������ȸ����µ�Trillium(��6��)��AlphaChip������˸��õ�оƬ���֣����ṩ�˸�������岼��ͼ���Ӷ��ӿ���������ڣ������˸������ܵ�оƬ��

����ͼ��ʾ�˹ȸ�����TPU��AlphaChip��Ƶ�оƬ�������������v5e��v5p��Trillium

����ͼ��ʾ����TPU��������Ŷ����ɵIJ�����ȣ�AlphaChip��TPU������Ʒ�е�ƽ�����߳��ȼ��� ����ԭ����һ����ƣ�һ�߽��� һ����˵�������оƬ����������ӵ�ģ�顢����·Ԫ����ɣ�������Щ����������ϸ�ޱȵĵ������������� ���⣬�������ิ�������֯�����Լ��������ͬʱ���㡣 ������Ƶĸ����ԣ�60��������оƬ��ƹ���ʦһֱ��Ŭ���Զ���оƬ���ֹ滮���̡� �ȸ��ʾ��AlphaChip���з�����AlphaGo��AlphaZero�м�ȡ�˾��顣

������֪��ͨ�����ѧϰ�Ͳ����ۣ�AlphaGo��AlphaZero��0������Χ�塢��������ͽ����DZ�ڹ��� AlphaChipͬ���Dz����ˣ���оƬ�ײ�滮��Ϊһ����Ϸ�IJ��ԡ� �ӿհ�դ��ʼ��AlphaChipÿ�η���һ����·Ԫ����ֱ������������Ԫ���� Ȼ�������ղ��ֵ�����������ģ�ͽ����� һ��ȫ�µġ����ڱߡ���ͼ��������AlphaChip���ܹ�ѧϰ����ӵ�оƬԪ��֮��Ĺ�ϵ������оƬ֮����з�������AlphaChip����Ƶ�ÿ�ֲ����ж������Ľ���

��ͼ��������ʾAlphaChip��û���κξ��������£�����Դ��Ariane RISC-V CPU���롣 ��ͼ��������ʾAlphaChip�ڶ�20��TPU�����ƽ�����ϰ������ͬ�Ŀ顣 AI��ţ���ӣ�2ҳŨ�������� �����Ǵ��������������һ�£�AlphaChip������ѵ�����̡� ֵ��һ����ǣ������о���������Jeff Dean���ӣ����к���Ҫ��ȫ��Ũ����������ҳ�����С�

������������ͬ���ǣ�AlphaChip�ǻ���һ�֡�ǿ��ѧϰ���ķ����� ����ζ�ţ���������˸���оƬ���������ʵ��ʱ�����ø��á����졣 ����Nature���ģ�2021�꣩���Լ�ISPD 2022�����о��������۵�����������Ԥѵ����������������AI���ٶȡ��ɿ��ԡ����ֵ����ܡ� ˳����һ�䣬Ԥѵ��Ҳ��������LLM����Gemini��ChatGPT����ӡ����̵������� �Դ�ǰ�о������������ȸ�㿪Դ��һ�������⣬�����������������ķ����� �������ǿ���ʹ������⣬�Ը���оƬ����Ԥѵ����Ȼ��Ԥѵ����ģ��Ӧ�õ��µĿ顣

�������µ�AlphaChipѵ�����̣��о���Ա�ڿ���������Ԥѵ����20��TPU��ģ�ͼ��㣨checkpoint���� ��Ȼ������������κ�Ԥѵ����AlphaChip��������ǰ�ľ�����ѧϰ���Ӷ������ѧϰ��������⡣ ѵ���ͼ�����Դ����RL�����壨�κ�MLģ�ͣ���Ͷ��ѵ����������ʧͨ�������١� ���ջ�����ƽ�ȣ��������ģ�Ͷ�������ִ�е��������˾����ܶ���˽⣬������־��ǡ��������� ��ѵ�����������ǻ���ѧϰ�ı�������������������·���������ܻ���ģ�͵����ܡ� AlphaChip��������Ӧ�õļ�����Դ����չ����ISPD 2022�����У��ȸ��Ŷ�����һ��̽������һ���ԡ�

���ĵ�ַ��https://dl.acm.org/doi/10.1145/3505170.3511478 ����Nature�������������ģ��ڶ��ض��������ʱ��ʹ����16��������Ԫ��ÿ����Ԫ��1��GPU��32��RL������ɣ�ͨ������̴�������10��CPU�� ����֮���ý��ٵļ�����Դ���ܻ������ܣ�������Ҫ�����൱����ʱ�䣬����ʵ����ͬ���������ܡ� ��ʼ����������Nature��������������֮ǰ���Ŷ�ʹ�������������ۺϵĽ��Ƴ�ʼ���֣��Խ��hMETIS����Ԫ��Ⱥ��С��ƽ������⡣ RL��������Ȩ���ʳ�ʼ���֣����Ҳ����ӷ��ñ���Ԫ�� ������ˣ��ȸ������ǽ�����һ�������о����ų����κγ�ʼ���ֵ�ʹ�ã�����Ҳû�й۲쵽AlphaChip�����½��� ���±�1��ʾ�� ������˵�����������˵�Ԫ��Ⱥ����ƽ���һ�������ǽ�hMETIS��Ⱥ��ƽ��������͵�������ã�UBfactor = 1���� �ɴˣ���ʹ��hMETIS���ɸ�ƽ��ļ�Ⱥ��

����Nature�����У��о���Ա������10nm�����Ƴ̵�TPU�����ʵ��ó��Ľ���� ��������ڵ�Ĵ�С�������ִ�оƬ�ĵ��ͳߴ硣֮ǰ�������ı����У����ý����45nm��12nm�� ��������ƽǶ����������ֽ��ϵļ����ڵ�ߴ��оƬ�����������IJ�ͬ�� ���磬��10nm���µ�оƬ�У�ͨ��ʹ�ö���ͼ����ƣ�����ڽϵ��ܶ��µ��²���ӵ�µ����⡣

��Դ��Pushing Multiple Patterning in Sub-10nm: Are We Ready? ��ˣ����ڽ���ļ����ڵ�ߴ磬AlphaChip������Ҫ�����佱���������Ա���õ���Ӧ������ չ��δ����AI���ı�����оƬ������� �Դ�2020�귢��������AlphaChip�Ѿ�������ÿһ���ȸ�TPUʹ�õij���оƬ���֡� ����˵��������Ϊ��������ʹ���ģ�Ŵ����Transformer�ܹ���AIģ�ͳ�Ϊ���ܡ� ��������Gemini������LLM������Imagen��Veo������ͼ�����Ƶ�������У�TPU��λ�ڹȸ�ǿ�������ʽAIϵͳ�ĺ��ġ� ���⣬��ЩAI������Ҳ���ڹȸ�AI����ĺ��ģ��ⲿ�û�����ͨ���ȸ��ƻ�÷���

�ȸ��������ĵ�һ��Cloud TPU v5p AI���������� ��ȸ�������콢TPUоƬ���Ѿ���������ص��������������졢���� ����ÿһ��TPU�ķ�չ��AlphaChip������ר��֮������ܲ������� ��TPU v5e�е�10��RL����ģ���3.2%�IJ��߳��ȼ��٣���TPU v5p�е�15��ģ���4.5%�ļ��٣��ٵ�Trillium�е�25��ģ���6.2%�ļ��١� AlphaChip��Ϊ��������CPU��Axion���ȸ���δ����������оƬ�������˳�Խ����IJ�����ơ� ��������˾��Ҳ�ڹȸ��о��Ļ����Ͻ����˸Ľ��� ���������ƾͲ�����AlphaChip���������Ƚ�оƬ�Ŀ��������ڹ��ġ����ܺ�����϶�оƬ�����Ż��� ���AlphaChip������һ����ʼ�� �ȸ��δ�������˴��룺AI��ʵ��оƬ���ȫ���̵��Զ����� ͨ�������㷨�Լ�Ӳ���������ͻ���ѧϰģ�͵Ķ˵���Эͬ�Ż���оƬ��Ƶ����ڻ������ӿ죬����������ܵ������� �ȸ��ʾ���dz��ڴ�������������ʵ��AIоƬ�Լ�оƬAI֮��ıջ��� ������Դ������Ԫ |

ԭ����Ŀ

IT�ٿ�

��������

�۳�ֵ•��ѡ

-

- ������HiVi��M200��ԴHiFi���� ����2.0�������� �ʼDZ�̨ʽ�������� ���ÿ�����������

-

��1079.1

��1199.0

- ���գ�HP��HyperX��Ӱ����PRO 16��Ϸ���ʼDZ�����U7-255HXRTX5060 16G 1T QHD 240Hz ����200W+

-

��12498.0

��12498.0

- Haida�����¿�UV��95mm�˾�NanoPro U-LR 1%������99.9%����52������Ĥ���������������������

- ��100��5

-

��555.0

��615.0

- ���س���APP��֬�ӵ��ӳӳ����سӼ���ר�����ܾ�����������ü���ר�����������ӳ����س� �������APP��֬�� ��� �غ�ֻ�����

- ����1w+

-

��26.99

��27.0

- �� DJI O4 Air Unit ϵ���콢������FPVͼ�� 4K�����֡������ ���ʵ���ʱԶ����ͼ�� ���˻���� DJI O4 Air Unit Pro

- ����1w+

-

��1499.0

��1499.0

-

- JBL��������ͬ�������LIVE780NC����Ӧ���������������� ͷ��ʽ����ʽ �ܱ� ƻ����hoho����6.0 ���ذ���Ʒ��LIVE780NCƻ����

- ȯ��ʡ0.9

-

��1231.0

��1367.8

- ��Ϊ��HUAWEI��FreeClip ���ж��� ����ʽ������������ �����ȹ���� ������ �������� �ǿպ�

-

��799.0

��899.0

- �߲ʺ磨Colorful��ս�� GeForce RTX 5060 Ti ������ 8GB GDDR7 DLSS 4.5 �羺����Ϸ��Ƶ����Կ�

- ����Ʒ

-

��3129.0

��3179.0

- ��ɫ��ESR����ƻ��15W���߳䡿magsafe������������iPhone17promax/16/15/14/13/12/��Ϊ�ֻ������������� ��ƻ��15W���߳䡿�ǿ���حMagsafe����

-

��25.0

��109.0

- ���գ�HP����Ӱ����11��Ϸ���ʼDZ����� ���Ҳ�����R9 8945HX RTX5060 16G 1TBSSD QHD240Hz��

- ȯ��ʡ300

-

��8498.0

��8798.0

-

- ����USB/Type-C3.2���ٶ����� SD/TF3.0˫�����õ���ƽ���ֻ���pocket4/3���˻�ƻ��17�˶����

- ȯ��ʡ0.88

-

��43.91

��49.9

- vivo Pad5 ���� 12GB+256GB չ��ͼ ���Ҳ���15% ����������9300+ 12.1Ӣ����������� ƽ�����

- ����1w+

-

��2649.0

��2849.0

- �����ã�Nintendo�������ڱ�˰�֡�Alarmo���� ��������� 35����������������ϷԪ�� ԭװ�հ�Alarmo���� �ٷ�����

- ȯ��ʡ10

-

��548.0

��598.0

- ��Ϊ��ͯ�ֱ� 5X Pro��Ϊ�ֱ������ֱ����߶�λ�绰������

- ȯ��ʡ100

-

��1298.0

��1398.0

- ����������Y7000 AI�߾� �羺��Ϸ�ʼDZ�����(Ultra7 255HX 16G 1T RTX5060 2.5K 180Hz ��) ���Ҳ���

- ����3000+

-

��8999.0

��8999.0

-

- ��ţIT20 ���������С����ѥ�ӿڻ��������С������������Ӱ���������� ����ɫ��ʿ�桿

- ȯ��ʡ10

-

��214.0

��239.0

- iKF Nano�ռ���Ƶ�桾�����Ƽ�|56dBǿ�����롿ͷ��ʽ���������������������֤�������߶�����

- ȯ��ʡ0.9

-

��413.1

��459.0

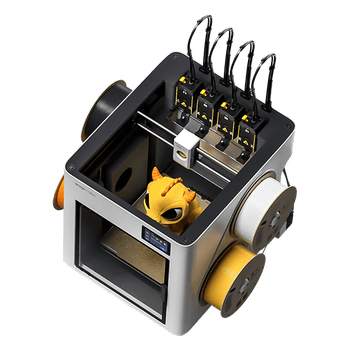

- SNAPMAKER����U1 3D��ӡ������4��ͷ��ɫ����ϸ߾��ȴ�ߴ�AI���ܼ�����������ٴ��ְ�ģ��5��ʡ��

-

��5399.0

��5999.0

- � D610 D750 24-120�� ȫ�������嵥������������۰��ж˵��� �걣����D610+24-85��ͷ �ٷ�����

- ȯ��ʡ220

-

��4772.0

��4992.0

- ����ʼDZ�����С��Pro16GT���ܱ� ���Ultra5 32G 1T 2.8K 120Hz OLED �����ᱡ�칫�� ���Ҳ���

- ȯ��ʡ80

-

��7299.0

��7799.0

����Ԫ

����Ԫ